天津理工大学计算机组成原理期末知识点总结

1,冯诺依曼计算机组成:运算器,存储器,控制器,输入设备,输出设备

==========================================================================

2,总线是如何分类的:按部件不同,总线可以分为

片内总线:芯片内部的总线

系统总线:CPU,主存,I/O设备各大部件间的信息传输线

数据总线:传输各个部件中的数据信息,双向传输,其位数和机器字长,存储字长有关

地址总线:指出数据总线上目的数据在主存单元的地址,单向传输

控制总线:发出信号使各个部件可以在不同时刻占用总线的使用权

通信总线:用于计算机系统与计算机系统,计算机系统与其他系统间的通信

串行通信:数据在1位宽的传输线上,一位一位地传输,适用于远距离传送

并行通信:将串行通信并列执行,适用于30m内的传输

3,为什么要设置总线的判优控制(仲裁):解决多个部件同时申请时的使用权分配问题

主设备:对总线有控制权

从设备:对总线没有控制权,只能响应主设备发来的总线命令

4,常见的总线集中式控制有那些:有三种,

链式查询:只需要很少的几根线就能按一定优先次序实现总线控制,并且很容易扩充设备,但对电路敏感,级低的设备很难获得请求(连线简单,易于扩充,对电路故障敏感)

计数器定时查询:多了一组设备线,少了一组总线同意线,优先级设置比较灵活,对故障不敏感,连线及其控制过程复杂

独立请求查询:速度最快,但硬件器件大,连线多,成本较高

5,通信的控制方式

总线的周期:

申请分配阶段:多个主设备申请总线使用权,总线仲裁绝对给其中的一个设备使用

寻址阶段:主设备发出地址信号,唤醒参与活动的从设备

传数阶段:主设备和从设备进行数据交换,数据流入目的设备

结束阶段:主设备的有关信息从总线上撤销,让出总线的使用权

同步通信:通信双方由统一时标控制数据传送

优点:规定明确,统一,模块间的配合简单一致

缺点:主从模块时间配合属于强制性同步,必须在规定时间内完成规定要求

例题:P61(总线的数据传输率=总线的宽度/总线的传输周期

一个传输周期可能包含多个时钟周期,1字=4字节=32位)

异步通信:主模块发出请求后,一直等待从模块反馈回来的响应信号后,才开始通信

不互锁方式:主模块发出请求,一段时间后确认从模块收到,撤销信号。从模块接到请求后,根据条件发出响应,一段时间后,确定主模块接收回答信号后,撤销信号

半互锁方式:主模块发出请求,必须接到从模块的回答信号后,才撤销请求信号,从模块一段时间后自动撤销信号

全互锁方式:主模块发出请求,必须接到从模块的回答信号后,才撤销请求信号,从模块等待知道主模块请求信号已撤销后,才撤回回答信号

半同步通信:同步异步结合,适用于系统工作不高,但又包含了由许多工作差异较大的各类设备组成的简单系统

分离式通信:充分挖掘系统总线每瞬间的潜能,

1主模块申请占用总线,使用完放弃总线的使用权

2从模块申请占用总线,将各种信息传送到主总线

6,总线带宽:总线数据传输速率=总线的宽度/总线的传输周期

7,画图说明异步穿行传输方式P63

============================================================================

1,为什么要加Cache:主存用来存放数据,其速度与CPU数据差距过大,为了让他们的速度很好的匹配,加入缓存

2, 缓存——主存:解决CPU和主存速度不匹配问题

主存——缓存:解决存储系统的容量问题

3,主存各个存储单元的空间位置是由单元地址号来表示的,而地址总线是用来指出存储单元地址号的,根据该地址号,可以读出或写入一个存储字

4,存储器的性能指标P74:

存储容量=存储单元个数 * 存储字长(位) 存储容量=存储单元个数 * 存储字长/8(字节)

例如:机器主存量为256M,它按字节存储的地址线位数对应28

存储速度:由存储时间和存取周期表示

存储器带宽:单位时间从存储器进出的信息最大数量

计算:如存储周期为500ns,每个周期可以访问16位,带宽=16/500ns=32M位/s

提高的措施:

1,缩短存储周期

2,增加存储的字长,使得每个存储周期可以读写更多的位数

3,增加存储体

5,存储器芯片:

存储器芯片通过地址总线,数据总线和控制总线和外部 连接

地址线是单向输入的,位数和芯片的容量有关

数据线是双向的,位数和芯片可以读写的数据位数有关

例如:地址线10根,数据线4根——》芯片容量为2^14=4k

片选线CS,CE 读写控制线WE(低写,高读)OE(允许读)WE(允许写)

片选线有效,芯片才工作

半导体存储芯片译码驱动方式:线选法,重合法

6,动态RAM的刷新P86:

什么是刷新:对DRAM定期进行的全部重写的过程

刷新的过程:实质上是将原信息读出,再有刷新放大器形成原信息并重新希尔的再生过程

为什么要刷新:电容上的电荷只能存活1~2s,由于存储单元的访问是随机的,有可能某些存储单元长期得不到访问,其存储单元内的原信息就会慢慢消失,因此需要在一定时间内对RAM的全部基本单元电路进行刷新,一般时间取2ms(再生周期)。刷新是一行一行进行的

集中刷新:在规定的一个刷新周期内,对全部存储单元集中一段时间进行刷新,此时必须停止读写操作,如对28*128矩阵的 存储芯片进行刷新,存取周期为0.5us,刷新周期为2ms=2000us。

对128行集中刷新需要128*0.5us=64us(死时间),2000us-64us=1936us用来读写,维持信息。

死时间率=64us/2000us=3.2%

分散刷新:对每行存储单元的刷新分散到每个存储周期内完成(在每个读写周期后插入一个刷新周期)。如对28*128矩阵的 存储芯片进行刷新,读写周期为0.5us,存取周期为1us。128行,每行1us

128us后完成刷新——》不存在操作死时间,存储周期变长了

异步刷新:集中式和分散式的折中,既缩短了死时间,又充分利用最大刷新间隔为2ms的特点

如对28*128矩阵的 存储芯片进行刷新,刷新最大周期为2ms=2000us。可采取在2ms内对128行,进行刷新,2000us/128=15.6us刷新一行,每行刷新时间为0.5us。死时间为0.5us

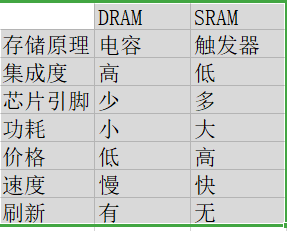

7,动态RAM和静态RAM的比较:

8,存储器与CPU连接

位扩展:增加存储字长(房间的大小)CS,WE一样

例如 2片1k*4位——》1片1k*8位:图P92

字扩展:增加存储器字的数量(房间的数量)WE一样,CS反向

例如 2片1k*4位——》2k*4位:图P93

字,位扩展:既增加存储字长,又增加存储字的数量

例如 8片1k*4位——》4k*8位:图P93

例题P95

9,分级存储的目的:解决存储容量,价格和存储速度之间的矛盾

10,Cache做在CPU芯片内的好处:

提高外部总线的利用率,CPU访问cache不需要占用外部总线

增强了系统的整体效率

提高存储速度

11,将指令Cache和数据Cache分开的好处:

可以支持超前控制和流水线控制

指令Cache可用ROM实现,提高指令存取的可靠性

数据Cache对不同数据类型的支持更加灵活

13,循环冗余码P144

=======================================================================

1,计算机中参与运算的数有:

无符号数:寄存器的位数反应无符号数的范围(机器字长16,无:0~65535)

有符号数:机器数的真值(-32768~+32768)

2,原码:把+看成0,-看成1

+1110——》0,1110

-1110——》1,1110

反码:(正)与原码一致 (负)符号位不变,数值位取反

0,1110——》0,1110

1,1110——》1,0001

补码:(正)与原码一致 (负)符号位不变,数值位取反,加一

0,1110——》0,1110

1,1110——》1,0010

3,已知【Y】补 求【-Y】补

将【Y】补的所有位取反,末位加一

4,因为补码很难在形式上比较大小,所以出现了移码

【x】移=2^n+x

两个数的减法:A-B= A+[-B]= [A]补+[-B]补(mod2^n+1)

两个数的加法:A+B= A+[B]= [A]补+[B]补(mod2^n+1)

5,

============================================================================

1,寻址方式:确定本条指令的数据地址,以及下一条要执行的指令地址的方法

立即寻址:形式地址A里面是操作数x

直接寻址:A存的是x在主存中的地址

隐含寻址:形式地址A里面是操作数x1,加上ACC中的x2——操作数x

间接寻址:形式地址A里面是操作数地址EA,EA指向操作数x

寄存器地址:A中存的是寄存器编号(里面有操作数x)

基址寻址:A中的值加上BR寄存器中的值——地址EA——>x

变址寻址:基址寻址

相对寻址:A中存的值加上PC寄存器的值——地址EA——>x

堆栈寻址:

2,机器指令的格式:

需要考虑的因素:

操作类型:包括指令数及其操作的难易程度

数据类型:确定哪些数据类型参与操作

指令格式:包括指令字长,操作码位数,地址个数,寻址方式类型,指令字长,操作码的位数是否可变

寻址方式:。。。

寄存器个数:。。。

=========================================================================

CPU的组成:

寄存器:用于存放当前指令的地址,存放操作数

CU:可以发出各种操作命令序列的控制部件

ALU:负责算术运算,逻辑运算(只对CPU寄存器的操作数进行操作)

中断系统:处理异常情况和特殊请求

流水线性能:

1,吞吐率:单位时间内流水线完成指令的数量,最大吞吐率T(max)=1/t

例如流水线完成n条指令,对于m级的流水线,每一段的处理时间为t

实际吞吐率:n/(mt+(n-1)t)

2,加速比:指m段流水线的速度与等功能非流水线速度之比

流水线各段完成时间为t,完成n条指令在m段流水线上的时间T1=mt+(n-1)t

非流水线上时间T2=nmt

加速比S=nm/m+n-1

3,效率:流水线中各功能段的利用率

流水线各段完成时间为t,完成n条指令在m段流水线上的时间区T1=m(mt+(n-1)t)

非流水线上时间区T2=nmt

效率E=T1/T2=n/(m+n-1)=S/m

中断隐指令:不再机器指令系统中,由CPU在中断周期内由硬件完成的一条指令

1,中断周期:

保护程序断点:把当前程序中寄存器的操作数保存起来

寻找中断服务程序的入口地址:找到下一条要执行指令的地址保存起来

关中断:确保CPU之后的响应不受中断请求影响

=====================================================================

CU控制方式:同步控制,异步控制,联合控制,人工控制

多级时序系统:由节拍和机器周期组成

=======================================================================

微指令格式:P412例题

还没有评论,来说两句吧...