74160ENT引脚设计法接成100进制加法计数器

之前和大家分享了同步置数法和异步清零法, 这里再和大家介绍另一种方法——ENT引脚设计法.

在开始设计前, 我们要明确ENT引脚和ENP引脚的作用: 当ENT=ENP=1时, 74160开始计数; 当ENT=0或ENP=0时, 74160处于保持状态. 这里我以ENT引脚(选择ENP引脚也可以)作为设计对象, 准备接成100进制加法计数器.

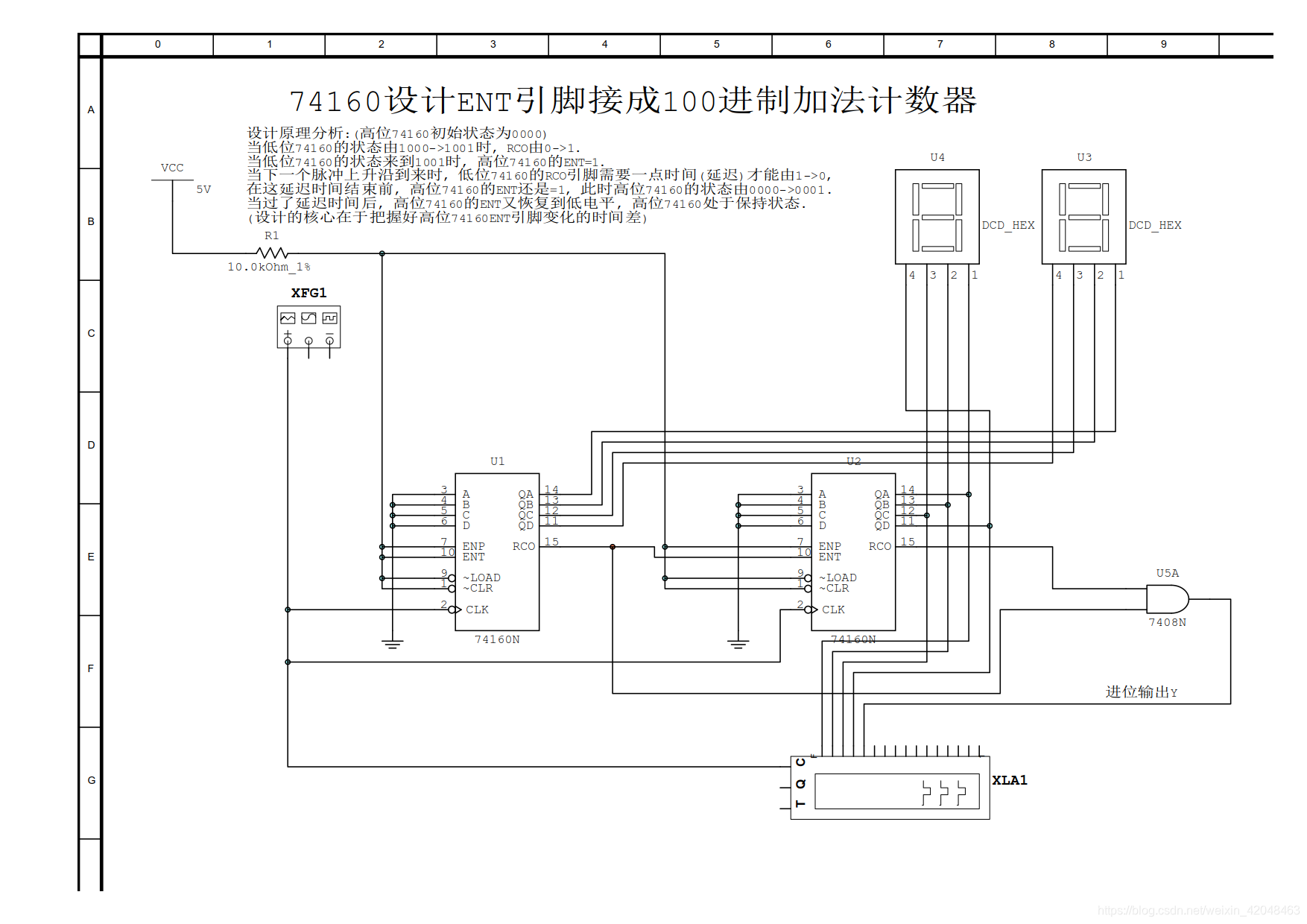

题目: 用2片74160、 1片与门接成100进制加法计数器.

分析(从下述电路图入手):

要接成100进制加法计数器, 重点在于处理低位74160从1001->0000时向高位74160提供进位信号的问题.

当低位74160到达状态1001后, 其RCO引脚变为高电平; 此时高位74160的ENT引脚也随之变为高电平. 当下一系统上升沿信号到来时, 两片74160的状态都+1, 而后低位74160的状态变为0000, 其RCO引脚随之变为低电平, 高位74160的ENT引脚也随之变为低电平. 当系统上升沿信号再次到来时, 低位74160依旧实现+1操作, 而高位74160由于其ENT引脚变为低电平, 则处于保持状态: 直到低位74160的状态再次到达1001时, 再次重复上述过程 .

如此设计的100进制加法计数电路, (比如)在09跳变为10时, 具有良好的视觉统一性: 而采用进位级联方式构成的100进制加法计数电路就不具备良好的视觉统一性(09跳变为10时, 低位先变, 高位后变).

还没有评论,来说两句吧...