PCB Allegro -04

1、出现的问题:

点击“+”后,

软件异常,找不到对应的page内容。

其它的工程文件正常。这个有时候提示“file is in use by other user````”

解决方案1:重新破解;—无效,问题依旧出现。

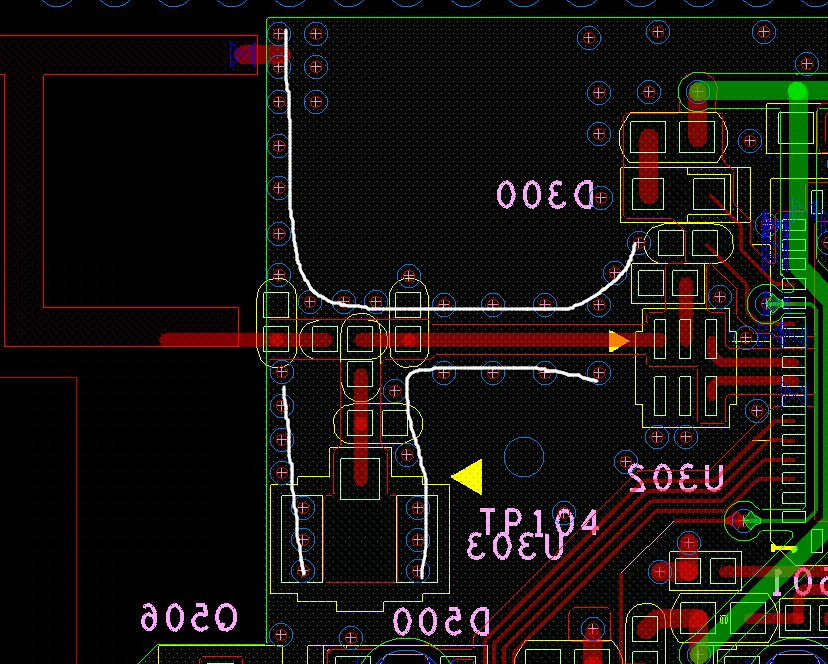

2、如何在Allegro中显示元件编号,如U1,R2.

打开Display—>Color—>Component—>Ref des,开启silkscreen,但是图中只是部分显示了编号。

流 水 笔 记:

12月3日,网络上于博士之cadence快速入门教材。系统的学习原理图和pcb,主要是cadence的使用。

12月25日,重新温习了一下orcad的使用。

Allegro中没有找到泪滴teardrop,不过找到的是fillet,和泪滴的功能一样。route->gross->add /delete fillet. 无论加泪滴还是删掉泪滴,一定要先打开所有的走线层,否则,没打开的走线层就不会有执行

ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline光绘设置详解http://www.flyarm.com/bbs/viewthread.php?tid=28&page=1 ALLEGRO 标注

1). dimension linear : 对于比较规则,简单的板子,通常采用.

2).dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。Manufacture——dimension/draft —–dimension linear / dimension datum

实时显示走线的长度Setup—user Preferences Editor栏中Route栏选择Connect—> ALLEGRO etch length on.

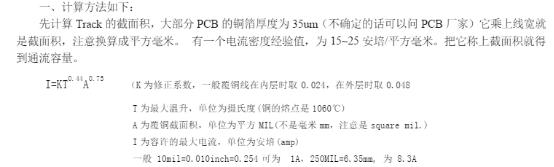

线宽与电流的关系:通常1oz的铜,10mil线宽最大电流1A,20mil-1.3A,具体参见下表。

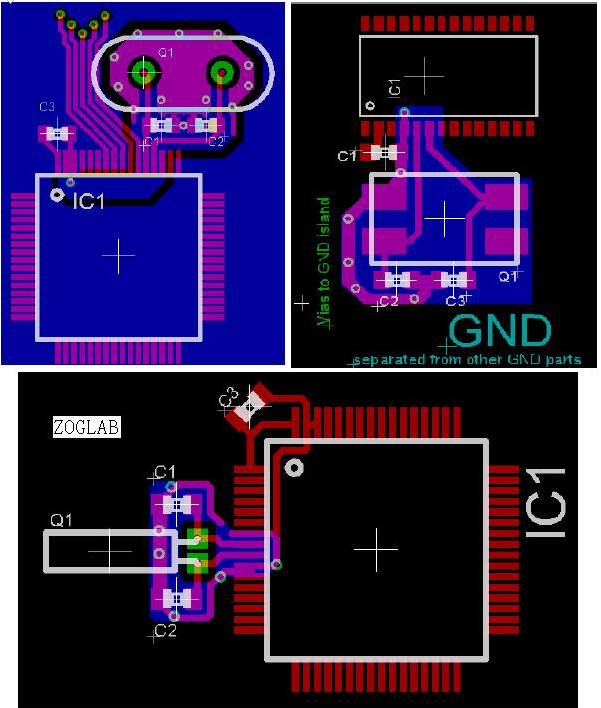

- 晶振/晶体走线:

1、有源晶振一般可以走过孔,但是晶体则不会。

2、通常需要包地处理,包地间距一般10mil。但也有要求晶振下面挖空处理的。

3、晶振选择上尽量选择4pin的带有金属屏蔽的晶振,一般精度10%左右或是5%更好。

4、晶振下面一般可以走电源线。(因为晶振外面的金属外壳屏蔽的很好)

5、布线尽量短,原理digit IO信号线,减少寄生电容对晶体的精度影响。

6、等长要求一般不需要,IC的Datasheet除非特别说明。

两种走线方式比较,方式1等长类似于差分信号走线。方式2-最短要求以及焊盘连接方式不同。两种方式都可以,最好是包地处理。

包地的话,最好留一个缺口,用地线地孔画个包围圈就好。

有时晶振外壳也会接地。增强抗干扰能力。通孔型晶体,两面都布置GND层最好,就像MSP430,如果没有这个gnd层,性能差很多。

通常布线时,power以及gnd采用铺铜的方式。

铺铜的目的是:减小阻抗,从而减小电流回路面积;大面积铺铜可以屏蔽的作用,保护信号免收干扰;另外可以减少板压变形。

而包地的目的是减少与临近信号之间的串扰,可以使用GND铺铜方式进行。注意包地与被保护信号的gap。

射频信号底部是一块完整的铺铜GND,提供完整的参考层,

同一信号层周边不走其它信号组线。

另外是注意信号走线周边的包地过孔。

还没有评论,来说两句吧...